RAMS[22] ハザード分析

安全を担う装置を開発するときは必ずハザード分析をしなさいと言われます。しかし、真摯にハザード分析をした人は意外と少ないのではないでしょうか。RAMS規格にも書かれていますが、ハザード分析の手法でHAZOPを使いなさいとか […]

RAMS[21] 電車内でのテロ行為

2021年10月31日午後8時ごろ、東京都調布市の京王線国領駅付近を走行中の電車で乗客から「車内で油のような液体をまいて男が火を付け、刃物で人を刺す」という事件がありました。電車内での犯罪や、テロ行為は海外だけではなく日 […]

RAMS[20] ISAによるSA評価

鉄道では開業の許可にISAによる安全性評価が必要なことが多いです。最終的なOKは各国の認可機関が開業にGOサインを出すのですが、その時に必要なのがISAによるRAMS規格適合性評価レポートです。RAMSというとSIL4認 […]

RAMS[19] GAの変更

鉄道信号の場合、Safety Platformから開発した各サブシステムのGA、例えば、VOBC(車上制御装置)、ATP地上装置や連動装置などを開発したのち、このGAを使って実際の個々の現地システムに対応させることになり […]

RAMS[18] 実際はどうしたらいいか

RAMSは階層化を想定しているので、1からの開発を考えたときの規格になっています。なので、途中段階から実行しようとするとそもそも無理があります。現実には最終システムを想定して開発をゼロからやるケースはまれで、特に日本の企 […]

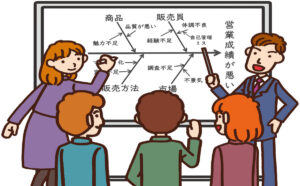

RAMS[17] 体制と組織

RAMS[9] 監視でRAMSのプロセスは監視が需要ですと書きました。では、具体的にどんな体制にしたらよいのでしょうか? 沢山の設計者がいる企業はいいかもしれませんが、小規模の会社はどうしたらよいのでしょうか?このブログ […]

RAMS[16] ランダム故障影響の数値要求 (IEC 61508 P2 7.4.5)

この章は「Random hardware failures (including soft-errors) and random failures of data communication processes」の二つの […]

RAMS[15] Hardware Safety Integrity (IEC61508 P2 7.4.4)

この章は正確には、「Hardware Safety integrity architectural constraints (アーキテクチャー上のハードウエアインテグリティーの制約)」です。これは、は安全機能の限界を決め […]

RAMS[14] アーキテクチャー以外の要求

I/Oやその他のアーキテクチャーはまた後で書くとして、 「後で書くという言葉が多いけど、本当にあとで書くんだろうか??? 忘れてしまっている気がする。(笑)」 タイトルにはアーキテクチャー以外と書いたけど、これもアーキテ […]