RAMS[13] アーキテクチャ

ハードウエアのアーキテクチャーと言っても色々あります。例えば、CPU、IO,ストレージなどそれぞれにアーキテクチャーが存在します。前述しましたが、IEC 61508の対象は。PROGRAMMABLE ELECTRONIC SAFETY-RELATED SYSTEMSですので、RAMSの殆どはこれらを想定しています。リレーなんかちょっと触れているだけです。なので、このアーキテクチャーもプログラマブルな電子機安全システムとして書かれています。信号リレーのように非対象動作でフェールセーフにすることができても、マイコンを用いてプログラムするアーキテクチャーではそのまま同じようにフェールセーフにすることはできません。

前述しましたが、非対処動作でフェールセーフが確保できない場合には、故障検知でフェールセーフを実現します。ただ、MPUの故障を検知するのはすごく大変です。まず、故障検知は一旦置いておいて、概念的な話から入ります。IEC 62425には機能の故障検知について書かれています。その方法は以下です。

- COMPOSITE FAIL-SAFETY

- REACTIVE FAIL-SAFETY

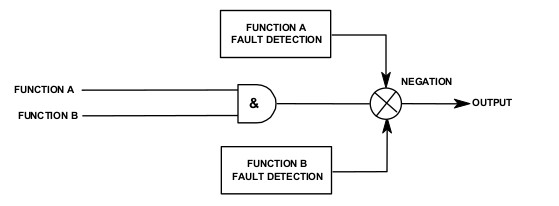

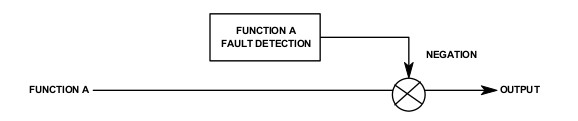

どちらもPE装置の場合の故障検知です。「COMPOSITE FAIL-SAFETY」二つの同じ機能(結果が同じことを期待) の独立した装置を用意して、同じ入力を入力しその結果を比較します。そして、その結果同じならばきっとその結果はあっているでしょうということで結果を使用します。「REACTIVE FAIL-SAFETY」は一つの出力を結果をチェック機能で結果をチェックします。結果が期待するものであればその結果を使います。なんか、おんなじことを言っているようですので、もう少し話をします。前者は全く同じ出力(FAULT DETECTIONから見れば入力)をするものを二つ、後者は1つが出力した結果を正しいかどうか判断する別の装置があり、その結果が正しくないと判断したらその結果は使用しません。例えば、温度50度のお湯を出す装置があって、その温度を別な装置が温度を測って、温度が50度であればお湯のバルブを開ける、みたいなものです。わかるかなぁ。なので、 「REACTIVE FAIL-SAFETY」 は簡単な機能に用いられ、 「COMPOSITE FAIL-SAFETY」 は複雑な機能に用いられます。したがって、PE装置だと必然的に 「COMPOSITE FAIL-SAFETY」になってしまいます。

これを説明すると大体言われるのが、「ではパソコンを二つ用意して結果を比較すればいい」ってことですね?

いいえ、違います。

これが成り立つためには内部の故障検知ができていることが条件です。ほかに条件もありますが、あとで書きます。結果があっているからいいじゃないか。とういう気持ちもわかりますが。では、もし、どちらも間違った同じ結果を出してしまったらどうでしょうか? 間違った結果を使いますよね。だから、駄目なんです。

私は「COMPOSITE FAIL-SAFETY」 の図を見て、FUNCTION A を出力する人、 FUNCTION B を出力する人が異なるのはわかりますが、FUNCTION A FAULT DETECTION を行う人と FUNCTION A FAULT DETECTION Bを行う人たちも独立である必要があるのかな?と思いました。が規格には

a) composite fail-safety

With this technique, each safety-related function is performed by at least two items.

と書いてあるので、二枚のCPUユニットでいけそうです。